Internal block diagram of 8255

RD (Read) : This control signal enables the read operation.

When this signal is LOW, the microprocessor reads data from a selected I/O port of the

8255A.

WR (Write): This control signal enables the write operation.

When this signal goes LOW, the microprocessor writes into a selected I/O port

or the control register.

RESET: This is an active HIGH signal.

It clears the control register and set all ports in the input mode.

CS, A0 and A1 : These are device select signals.

The CS is connected to the decoder in the system.

A0 and A1 are generally connected to A0 and A1 of the processor.

(Alternatively, A0 and A1 can be connected to any two-address lines of the processor).

8255 can be either Memory mapped or I/O mapped in the system.

A0 and A1 address lines can be made to select any one of the following four internal devices as shown on right side.

Programming 8255:

The 8255 has two control words, one for specifying 1/O functions and another for bit set/reset mode of port C. Both the control words are written in the same control register.

The control register differentiate them by the value of bit D7 .The bit set/reset control word does not affect the functions of ports A and B.

Bit D7 of the control register specifies either the 1/0 function or the bit set / reset function.

If bit D7 = 1, then the bits D6 – D0 determine 1/0 functions in various modes.

If bit D7 = 0, then the bits D6 – D0 determine the pin of port C to be set or reset.

The 8255 ports are programmed (or initialized) by writing a control word in the control register.

For setting 1/0 functions and mode of operation the 1/0 mode control word is send to control register. The format of the 1/0 mode set control word is shown below.

For setting/resetting (BSR mode) a pin of port C, the bit set/ reset control word is sent to control register. The format of bit set/reset control word is shown below.

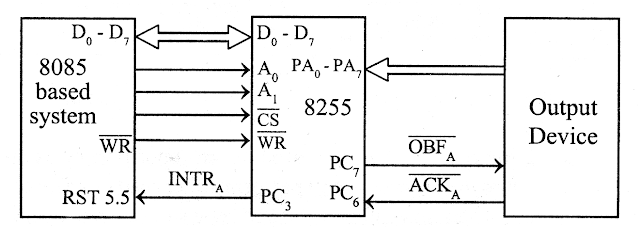

The data transfer between the processor and the port can be either interrupt driven or through status check.

In the interrupt driven data transfer scheme, when the port is ready, it interrupts the processor for a read or write operation.

In status check technique, the processor polls the status of the port and checks whether the port is ready for data transfer or not. The status of the ports A and B can be known by reading the port C. When the port is ready for data transfer, the processors executes a read or write cycle.

In the interrupt driven data transfer scheme, when the port is ready, it interrupts the processor for a read or write operation.

In status check technique, the processor polls the status of the port and checks whether the port is ready for data transfer or not. The status of the ports A and B can be known by reading the port C. When the port is ready for data transfer, the processors executes a read or write cycle.